microAptiv

MIPS microAptiv是现有最小,功耗最低的MIPS CPU系列。

与同类竞争的混合微控制器/DSP解决方案相比,microAptiv内核还具有更高的性能,在microMIPS模式下可提供1.7 DMIPS / MHz和3.44 CoreMark / MHz。

随着不断发展的受支持的第三方合作伙伴产品生态系统,以及一整套完善的MIPS开发工具,microAptiv提供了一个完整的环境来加速SoC设计并缩短产品上市时间。

microAptiv是一款高性能,紧凑型处理器,具有高级DSP功能。

microAptiv可以通过两种配置获得许可:

- 带有内存管理单元(MMU)和高速缓存的微处理器(MPU)

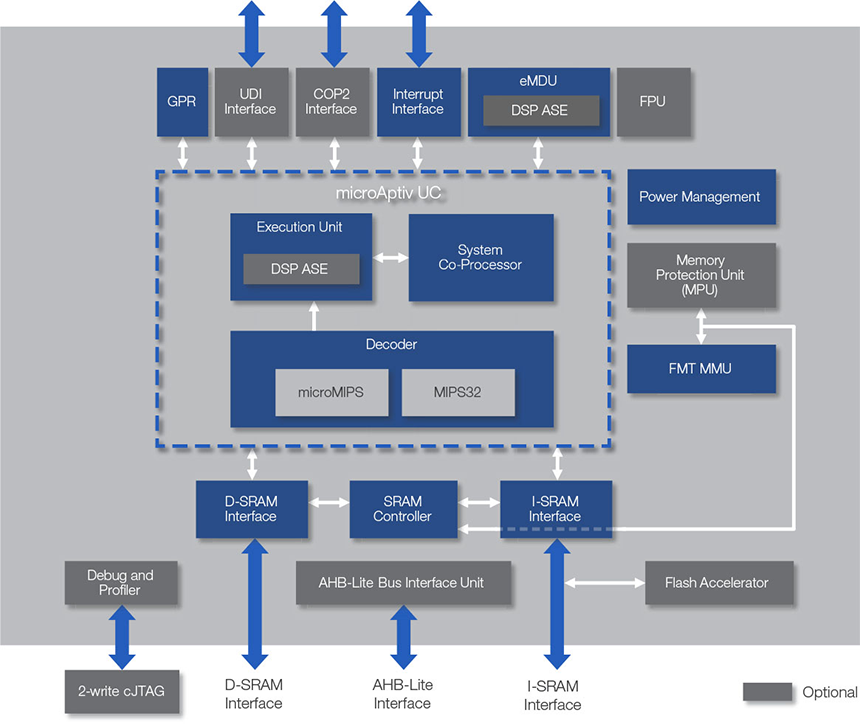

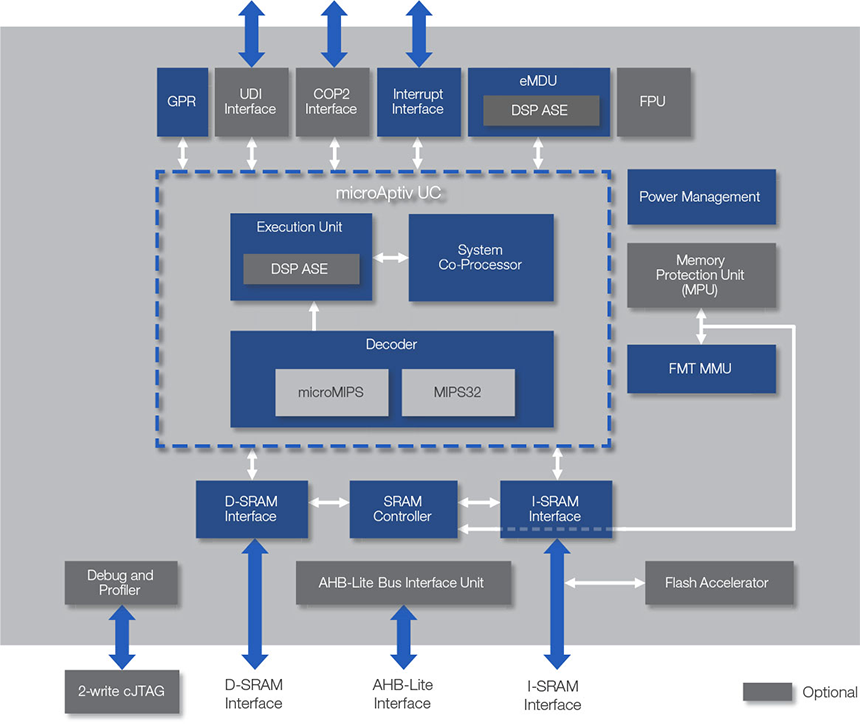

- 具有存储器保护单元(MPU)的微控制器(MCU)

microAptiv MCU

用于微控制器应用的MIPS32®M14K内核的无缓存实现和超集。

microAptiv MPU

MIPS32®M14Kc内核的超集,具有高速缓存控制器和内存管理单元(MMU),可帮助嵌入式系统设计执行执行丰富的操作系统来管理虚拟内存。

MIPS microAptiv 特点

MIPS32®M14Kc内核的超集,具有高速缓存控制器和内存管理单元(MMU),可帮助嵌入式系统设计执行执行丰富的操作系统来管理虚拟内存。

先进的DSP功能

通过添加MIPS DSP应用程序特定扩展(ASE)版本2,增强了microAptiv内核。microAptiv内核保留了M14K内核中的所有可用功能,包括microMIPS代码压缩ISA和MCU ASE,它们可提供实时性能和 微控制器和嵌入式系统设计开发的成本优势。

DSP ASE r2为microAptiv MCU内核提供了高性能,单周期吞吐量的DSP和SIMD功能,可满足需要更多信号处理功能的各种嵌入式应用的需求。 这些应用包括工业/电机控制,智能仪表,汽车,存储,移动通信和安全性。

安全调试

此外,microAptiv MCU内核集成了内存保护单元和安全调试功能,这些功能可在要求高安全级别的系统中使用。 microAptiv内核提供了大量的可配置性,包括选择在仅MIPS32模式,MIPS32 + microMIPS模式或仅microMIPS模式下运行。

通过添加低成本的2线cJTAG选项(IEEE标准1149.7),进一步增强了microAptiv内核的调试功能。