MIPS 微控制器 (MCU) 架构模块

架构模块

MIPS已开发出MCU体系结构模块,以扩展对中断控制器的支持,减少中断等待时间并增强微控制器系统设计中通常需要的I/O外设控制功能。 它首先在MIPS32 M14K处理器内核系列上实现,现在是microAptiv,M51xx和M62xx内核系列的一部分。

MCU模块支持MIPS32和microMIPS指令集架构(ISA)。

中断传送

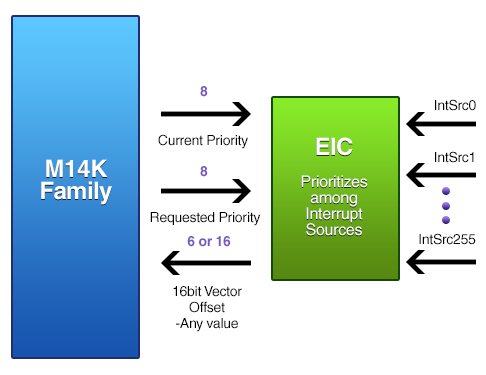

- 独立的优先级和向量生成

- 在EIC(外部中断控制器)模式下最多支持256个中断和8个硬件中断引脚

- 提供16位向量偏移地址

I/O 外围设备控制

包括原子位设置/清除指令,这些指令使I / O寄存器中通常用于监视或控制外部外围设备功能的位无中断修改,从而确保安全地执行操作。

减少中断延迟

- 预提取中断异常向量

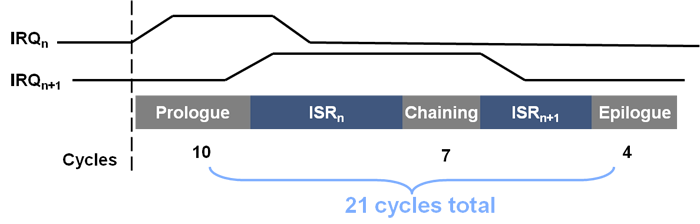

- 自动中断序言–在中断处理程序之前添加硬件以保存和更新系统状态

- 自动中断摘要–恢复先前存储在堆栈中的系统状态,以从中断返回。

- 中断链接–支持未决中断的服务,而无需退出初始中断例程,从而节省了存储和恢复多个活动中断所需的周期

- 支持中断向量地址的推测性预取。 通过将内存访问与管道刷新和异常优先级重叠来减少中断服务周期的数量