interAptiv

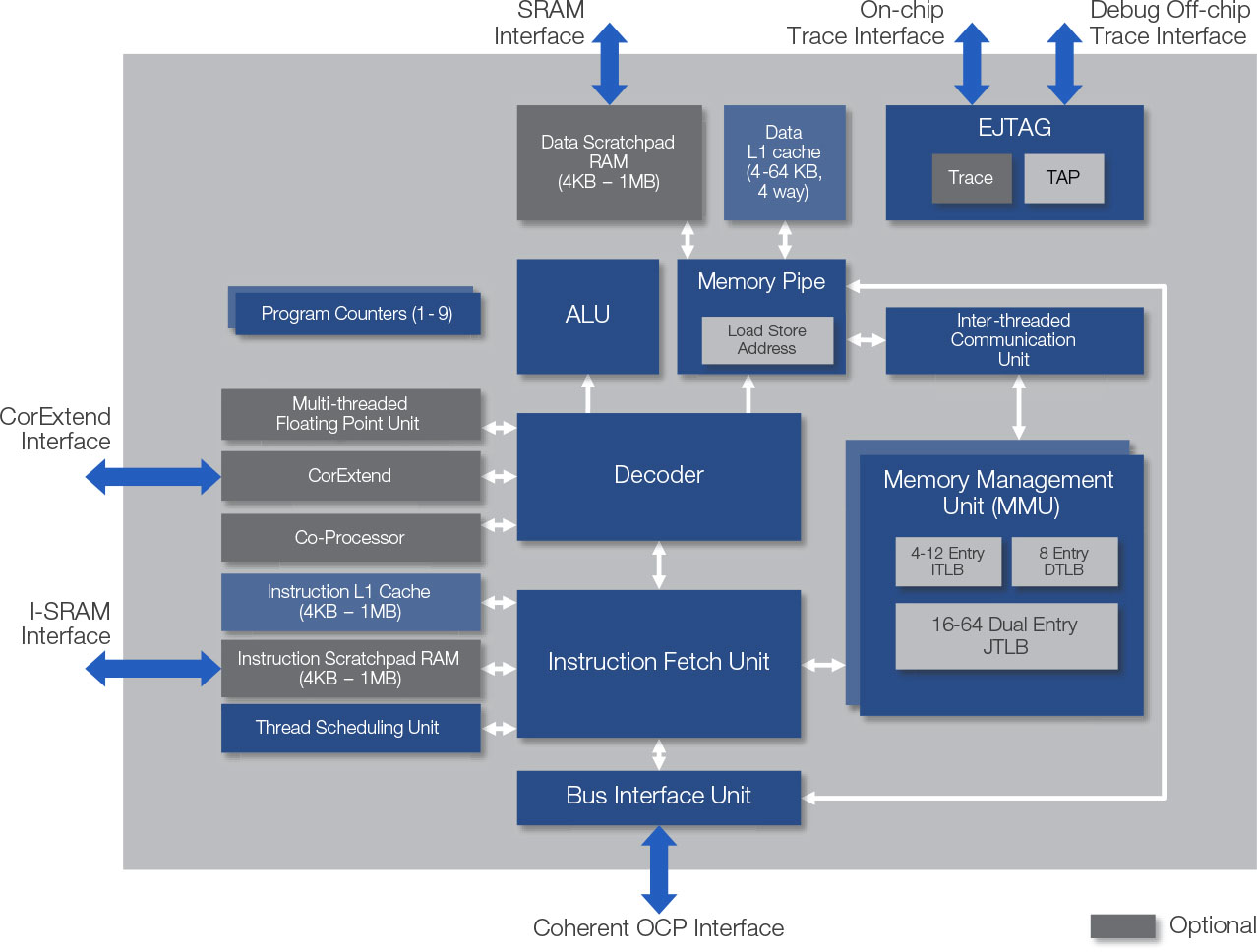

MIPS interAptiv是一个多核,多线程32位处理器家族。

多线程的使用,对多核性能的改进以及用于纠错和电源管理的其他内核增强功能使interAptiv成为同类产品中性能最高,功能最丰富的CPU内核。

使用MIPS interAptiv CPU,设计人员可以善用两个虚拟处理单元(VPE)或硬件线程,它们对于SMP(对称多处理)操作系统而言就像是两个完整的处理器。

这些线程有效地使用了共享的执行管道,相对于同类竞争内核而言,在面积和功耗方面都具有非常高的效率,这是通过行业标准CoreMark基准测试得出的。 还可以使用硬件调度程序和线程间通信功能来管理线程。 高效率和对线程级管理的访问权限使interAptiv CPU成为高度线程化且需要支持服务质量(QoS)的应用程序的理想解决方案。

MIPS interAptiv CPU利用第二代Coherence Manager(CM2)互连,该互连具有集成的L2缓存。 CM2通过同时减少延迟和增加带宽来提高多核性能。 CM2在单个完全一致的多处理器系统中最多支持四个interAptiv CPU或八个虚拟处理器。

随着越来越多的数据在各种嵌入式客户端设备和存储基础设施设备之间进行存储和传输,数据可靠性日益增长。 interAptiv CPU在数据存储器上具有错误校正码(ECC)支持,使其非常适合可靠性更高的应用程序,例如RAID存储和汽车驾驶员辅助。

interAptiv CPU具有强大的能力来控制群集和核心级别的电源,因此电源管理对于SoC设计人员而言是非常快速能使用的。