I-类 I7200

专为下一代高性能无线通信和网络设计的CPU IP

无线通信领域迎来崭新的5G世代,5G有望将数据带宽增加到现有LTE设计数量级或更多。 有许多技术和技术可用来应对这一挑战,但是大多数技术是基于增加系统中的并行性以实现网络上更高的总带宽目标。

更高的数据速率和并行处理不仅是LTE和5G市场以及支持这些通信目标的产品中的调制解调器所独有的。 由于处理技术的进步(摩尔定律被打破),未来在频率缩放方面的收益有限,因此,在更广泛的通信和网络市场中,许多应用都利用并行处理来应对不断增长的数据速率的挑战。

MIPS多线程多处理器IP内核

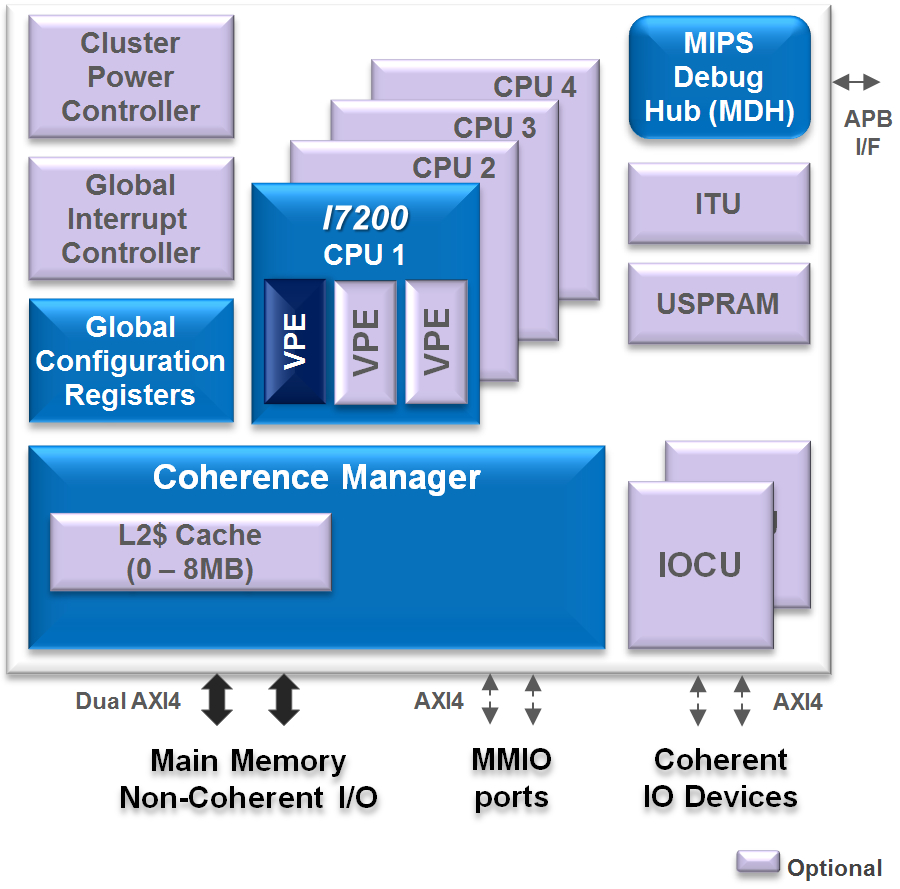

面对这些市场趋势和需求,MIPS I7200处理器内核基于硬件多线程和多内核集群CPU技术的基础,提供了高效,可扩展的并行处理性能。

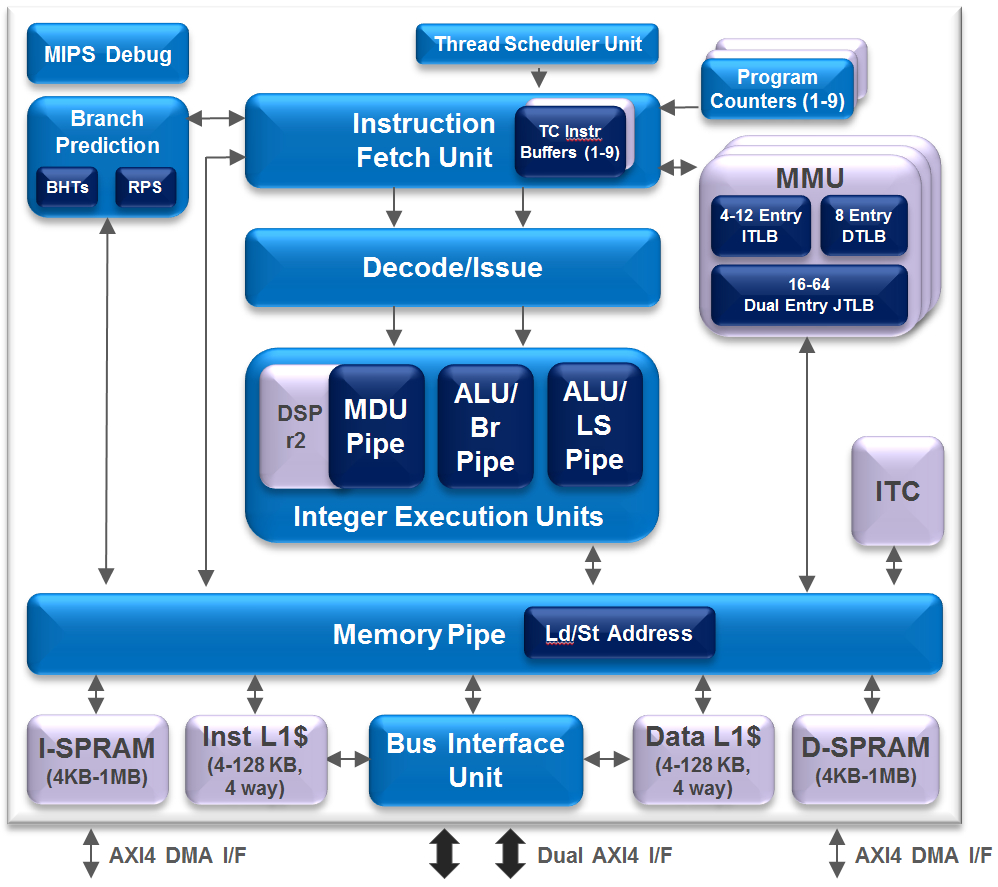

MIPS在2006年推出了其首个多线程CPU,并在2008年扩展了该多线程多核处理。基于十多年的专业知识,MIPS I7200是采用高性能和高效IP核的普及系列中的最新一代产品。这些技术。与上一代interAptiv™系列相比,它在性能上迈出了实质性的一步,在各种流行的基准测试中,性能提高了约50%,而核心尺寸仅增加了20%。 I7200是双发射超标量设计的,因此性能得到了提高,从而支持垂直多线程-每个时钟周期在一个线程上出现双发射,并且能够在多个周期之间的线程之间进行内文切换。

除了更高的性能外,多线程支持还可用于对高优先级和实时事件提供非常低的延迟响应。 对线程之间的零虚耗内文切换,硬件支持的优先级调度以及将线程分配给事件并将其挂起直到发生高优先级事件的能力的基础支持,为非常低的延迟响应提供了基础。

MIPS I7200也是MIPS系列产品中第一个实现nanoMIPS™指令集架构(ISA)的内核,该新版本的MIPS ISA旨在提供同类最佳的小代码尺寸,但又不牺牲当今应用程序所需的高性能 。 当针对性能进行编译(-O3编译标志)时,nanoMIPS的代码大小可比标准MIPS32小40%。

MIPS I7200 的主要功能/优点

- 具有垂直多线程(VMT)的双发射超标量设计:在各种基准上,性能提升了50%,而核心面积仅增加了20%。高效的面积和功率优化设计。

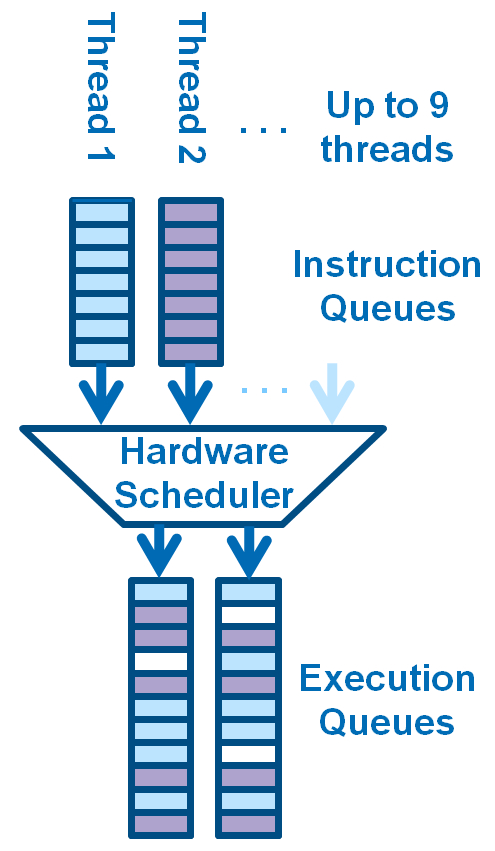

- 针对高优先级事件的实时,低延迟响应:零周期上下文切换,每个硬件线程的指令队列,硬件优先级线程调度以及确定性执行功能(例如ScratchPad RAM(SPRAM)),具有内存保护功能的简单直接映射内存访问可提供实时系统中极低延迟响应的基础。

- nanoMIPS™小代码大小ISA:在提供高性能的同时,实现同类最佳的小代码大小。编译代码以提高性能时(-O3标志,gcc编译器),可以在不牺牲性能的情况下将MIPS32的代码大小减少多达40%。

- 多线程多核处理:高度可扩展的并行处理平台,可满足应用程序的特定要求。 IP内核是客户可配置的,用于硅设计期间每个内核的线程数和群集中的内核数。并且在运行时,标准的SMP操作系统(RTOS或Linux)可以根据当前软件工作负载的需求来利用线程和内核。

- 可优化基于Linux或基于RTOS的软件开发的核心功能:诸如内存管理,缓存使用和/或ScratchPad RAM内存等功能的可配置选项。

MIPS I7200 基本核心功能

- 32-bit nanoMIPS™ 指令集架构

- 优化了可变长度指令集体系结构,以提供高性能的同类最佳的小代码量

- 包括MIPS DSP ASE –针对整数DSP和32位SIMD操作的优化指令集扩展

- 带有垂直多线程(VMT)的平衡的9阶段双发射管道

- 每个周期在单个线程上超标量

- 零开销内文切换–可以在每个时钟周期切换线程

- 实施MIPS-MT-ASE –每个内核最多可实现3个完全可见的虚拟处理器单元(VPE),每个内核最多可实现9个轻量线程内文(TC),可分配给VPE

- 可配置的内存子系统

- 支持缓存,紧密耦合的ScratchPad RAM(SPRAM)或同时支持两者

- L1缓存– 4路设置关联

- MPU的指令和数据高速缓存分别为0-128KB

- 每个具有0-64KB,带有完整的基于TLB的MMU

- ScratchPad RAM (SPRAM)

- 确定性的低延迟指令/数据访问和/或高性能数据处理以及在标准高速缓存存储器层次结构之外的搬移(例如,通过128b AXI-4接口将DMA直接移入内核的本地D-SPRAM)

- 每个0-1MB,用于指令,数据或统一的SPRAM实现,其中Unified可在集群中的CPU之间共享

- 可配置的内存管理

- 完整的基于TLB的内存管理单元(MMU),用于Linux和其他基于虚拟内存的操作系统

- 具有(最多)32个区域的内存保护单元(MPU)的更简单,确定性的直接内存访问,可与实时操作系统(RTOS)和裸机编程配合使用

MIPS I7200 多核群集功能

- 一致的多线程多核平台IP –包括构建完整的一致的多核系统的所有要素

- 一致性控制器(CM)

- 支持多达4个内核和多达2个硬件I / O一致性单元 (IOCUs)

- 集成二级高速缓存(L2 $):8路设置关联

- 高达8MB的内存

- 可配置的等待状态到RAM以实现最佳的L2 $设计

- 线程间通信单元 (ITU)

- 核心或群集中线程之间传递消息/数据的快速路径,更高效率的替代方案

- 全局中断控制器 (GIC) 最多256个中断

- 集群电源控制器 (CPC) 用于高级电源管理

- 多核集群中每个CPU的时钟和电压门控

- 本机AXI-4外部接口

- 双AXI-4主系统接口,用于单独的缓存(最大256b)和未缓存的访问(128b)

- 每个IOCU端口的128b接口

- 每个内存映射的低延迟I / O(MMIO)端口的64b接口

- 先进的调试功能–调试和跟踪

- 来自MIPS调试中心(MDH)中群集所有元素的聚合调试支持

- 支持APB界面集成到与Coresight™兼容的系统调试框架

效能测试基准和规格

| 每核 | 1个执行绪 | 2个执行绪 |

|---|---|---|

| CoreMark/MHz | 4.6 | 5.9 |

| DMIPS/MHz | 2.3 | 2.65 |

TSMC 28HPM

| TSMC 28HPM | ||

|---|---|---|

| 面积 | From 0.27mm² | Fully floorplanned, includes logic and 32K/32K L1$S |

TSMC 16FF+

| TSMC 16FF+ | ||

|---|---|---|

| 频率 | 1.7GHz (worst case), 2.1GHz (typical) | |

| 面积 | 0.27mm² | @ 1.7GHz implementation |

| 功耗 | 150mW (dyn) | @ 1.7GHz |

| CoreMark | > 40,000 | @ 1.7 GHz |

- Worst case = SS corner silicon, V = Vnom – 10%, T = 0C

- Typical = TT silicon, V = Vnom, T = 85C