I-类 I6400

MIPS I6400多处理器内核基于成熟的 MIPS64架构为广泛的市场和应用带来了历经淬炼以及一系列丰富且独特的功能。

I6400提供客户卓越的性能/效率水平,其设计具有引人注目且独特的功能,例如同时多线程(SMT),硬件虚拟化,128位SIMD,高级电源管理,多重内文安全性和可扩展性,以实现连贯的多集群操作。

丰富与独特的功能组合

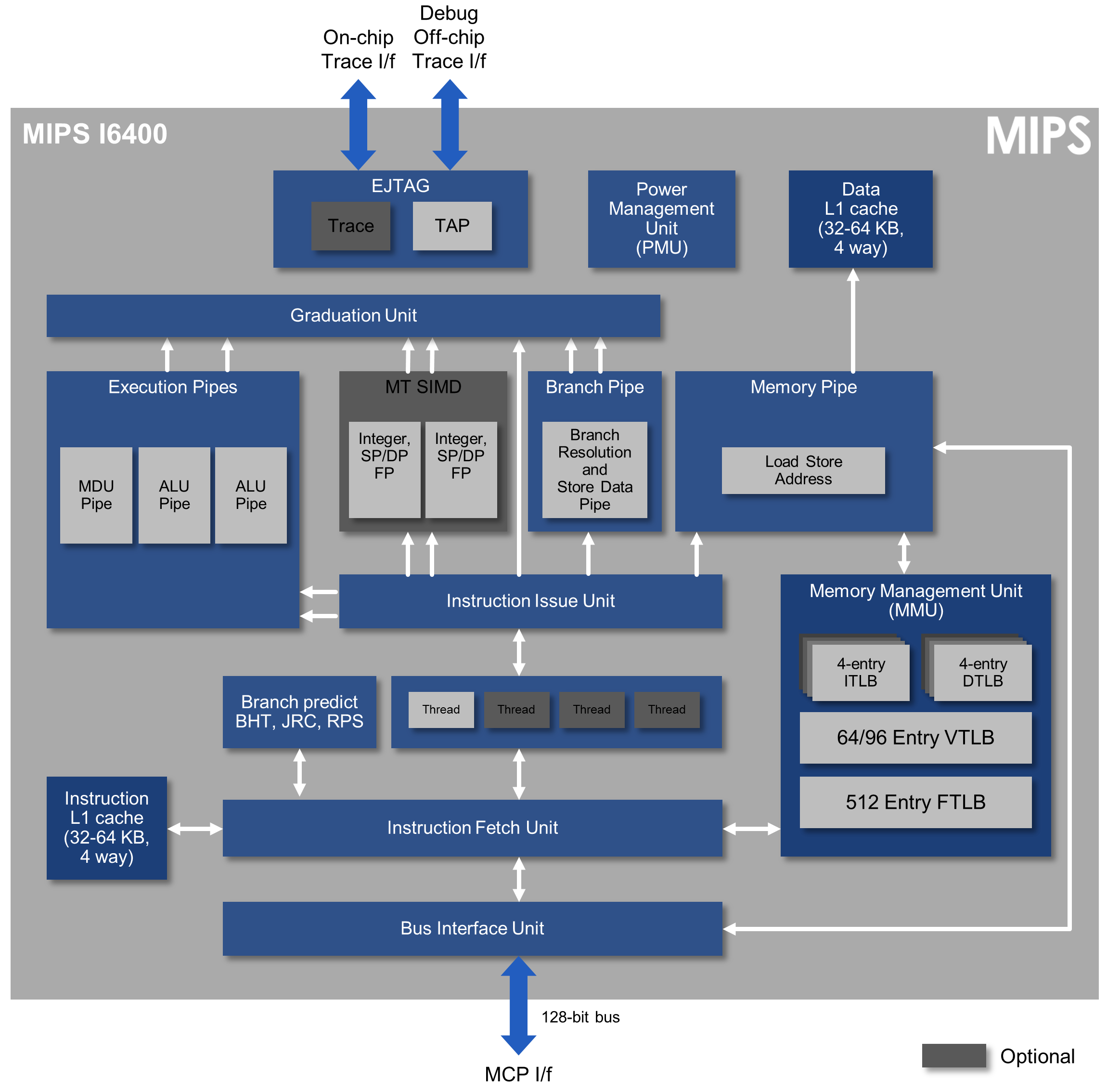

MIPS I6400 CPU是基于紧密的9级双发射流水线架构,并采用SMT为同类CPU内核中的性能效率树立新标准的设计标竿。 它可以作为完整可综合的RTL使用,从而允许在单个工艺节点中以及跨工艺实体结构的多种实现,并可重复使用。

升级的64位计算

I6400是完整的MIPS64处理器,可实现小尺寸与高性能的独特结合,远远超出了市场上其他64位中阶处理器内核。 但是,它的灵活性和效率也使其成为传统32位处理器IP内核的引人注目的替代品,甚至挑战了许多高端64位内核产品-但尺寸和功能却很小。

但是I6400的性能和效率特性仅仅是个开始。 I6400是基于最新版本的MIPS64架构版本6的MIPS系列产品中的第一个核心。

发行版6本质上是MIPS架构的简化,其目标是增强在更现代的软件工作负载上的执行力,这些工作负载包括即时编译器(JIT),虚拟机(VM)和位置独立代码(PIC)。 这些技术和构造通常可在Android,Javascript,浏览器和更新的编译器技术(例如LLVM)中找到。

此外,MIPS64是MIPS32架构的适当超集。 这样,MIPS64也可以直接运行MIPS32软件-无需单独的ISA或模式切换。

可实现异构计算

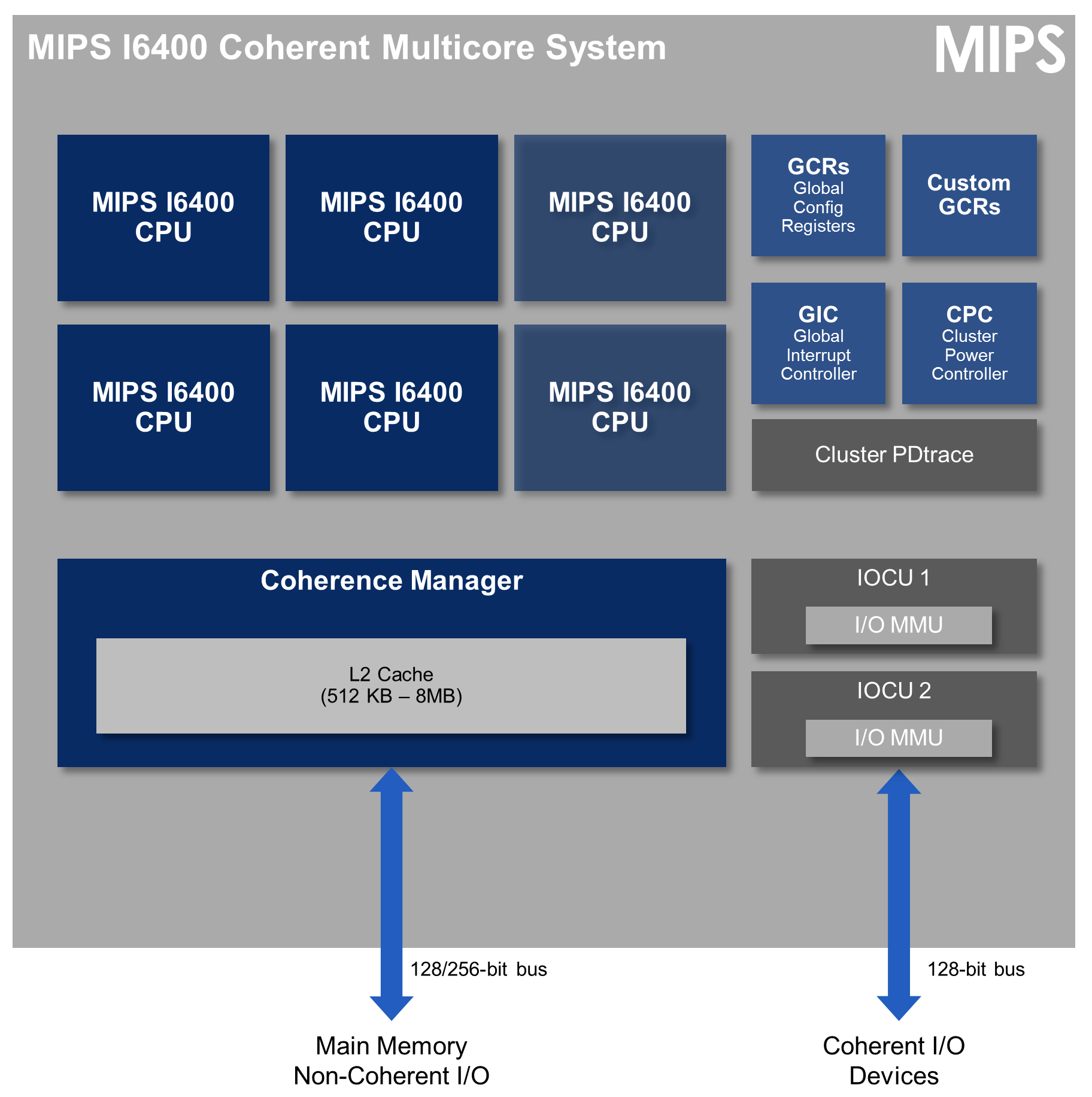

I6400设计用于多内核应用。 作为多核系统,它包括集成的L2缓存以及对全域中断和I / O一致性的虚拟化支持。

新的关键突破是相对于以前的MIPS多核产品而言,新的一致性管理方案已从基于监听法的一致性设计转变为基于目录法的一致性设计,并因此改善了功耗,性能和可伸缩性。一致性管理器(CM)可以在一个多核群集中最多支持六个核,并且该群集中的每个核都可以独立的时钟和电压级别运行,从而支持更多异构操作环境,并提供了全新的高级电源管理级别。新的CM还被设计为可扩展到一致的多集群实现中。

鉴于其小巧的性能,可直接支持MIPS32的MIPS64架构以及众多引人注目的和与众不同的新功能,I6400是可满足众多市场和应用需求的CPU解决方案。它可以用于许多具有MT和虚拟化以及ECC的核心系统中,这些系统运行用于从企业级解决方案的64位软件,一直到运行深度嵌入式应用程序的RTOS的单核或双核实施,以及介于两者之间的许多排列和市场。

独特的硬件虚拟化功能

通过支持硬件虚拟化,I6400加入了P5600和M5100 / M5150内核,以在MIPS Warrior一代内核产品系列中自上而下提供这项关键技术。 此功能支持虚拟化的更多传统用途,例如用于企业级应用程序的多OS系统,但也为IoT,可穿戴设备,消费类和移动应用程序的多内文安全解决方案奠定了基础。

I6400支持具有来宾和Root特权级别的完整硬件虚拟化,从而允许现有的MIPS软件和生态系统在来宾域内保持不变,并且具有Root特权级别的管理程序/安全内核控制。

高效的128位SIMD引擎

这个新的处理器内核还具有双发射和多线程 FPU/SIMD 单元, 非常适合于各种计算密集型任务,例如音频,视觉和视频处理。 标量和SIMD浮点功能完全符合IEEE-754 2008,并支持8 // 16- / 32- / 64位整数和定点数据类型以及16 // 32/64位浮点 数据类型。

性能基准

依据MIPS官方数据,I6400其性能表现在TSMC 28HPM制程技术中,一个完整配置的基本内核1的尺寸为1 mm21,可达到1 GHz(在最坏操作情况下使用slow corner硅条件测得),同时提供3000 DMIPS和5600 CoreMark2。

该处理器可在更激进的实现方式和操作条件下接近2 GHz。

- 基本核心配置是多核群集中的核心之一,包括32KB L1 $,完整的TLB,MT FPU / SIMD单元和虚拟化支持。 它不包括一致性管理器或L2 $或群集级别的功能。 所示的所有规格和基准数据均为初步数据

- 所示的所有规格和基准数据均为初步数据。 最坏的情况是,慢角条件假设慢/慢角硅以Vnom运行– 10%,Temp = 0C和8%OCV + 25ps时钟抖动裕量。 所引用的更具攻击性的实现和操作条件可能包括更高的性能库和内存,电压过载,典型的芯片以及更宽松的操作规范。

I6400 优势

- MIPS64是一种经过验证,成功且受到良好支持的64位架构,作为可许可IP内核为客户创造更多的价值。

- 提供引人注目的性能/功耗/面积比例,灵活性和功能,非常适合广泛的市场和应用,从深度嵌入到汽车到消费/移动,一直到企业级存储/服务器/数据平面解决方案。

- 用于企业/消费者分区,安全内容访问,支付/交易以及将安全方案与众多内容源隔离的多重内文安全平台。

- 广泛的软件和生态系统支持以及成熟的工具链。

- 可用作可合成IP,可在带有标准单元和存储器的任何工艺节点中实施。

- 128位SIMD-加速指令的执行,以高级语言(例如C,OpenCL)进行开发,从而加快了音频,视频,图形,图像,语音和其他面向DSP的软件算法的执行。

- MIPS 多域安全 技术–确保需要安全的应用程序彼此有效,可靠地隔离,并免受非安全应用程序的攻击。

I6400 基本内核功能

- 64位MIPS64版本6指令集架构

- 经过验证,成功且得到广泛支持的64位架构

- MIPS32的超集–可直接运行MIPS32软件

- 带有 同步多线程(SMT)的均匀9阶段双发射管道

- 每个周期在单个线程或两个线程上同时执行超标量

- 每个核心最多4个线程

- 指令绑定–将连续的整数或浮点加载或存储合并到一个操作中,从而提高内存密集型数据搬移代码最多增加2倍

- 硬件虚拟化

- 提供内核和用户空间的root和guest虚拟机特权级别

- 支持多个来宾(guest),每个来宾具有完整的虚拟CPU,亦即来宾OS无需修改即可运行

- 单独的TLB,root和guest虚拟机的COP0内文,提供完全隔离,快速内文切换,由root处理异常和中断

- 完整的SoC虚拟化支持(IOMMU和中断处理–请参阅多核功能)

- 可编程内存管理单元(MMU)

- 具有阵列的第一级和第二级TLB,支持可变和固定页面大小

- L1快取

- 具有ECC,4路设置关联的32KB或64KB的指令和数据快取

- 新型高性能双发射FPU / SIMD单元-可选

- 32 x 128位寄存器组,向SIMD单元加载/从SIMD单元存储128位

- 本机数据类型:8/16/32/64位整数和定点,16/32/64位浮点

- 符合IEEE-754 2008

独特的一致性多核处理器功能

- 完整的多核系统,旨在获得最大的群集级带宽

- 一致性管理

- 在一个集群中最多支持六个核心的多核心配置

- 新的基于目录的一致性方案–改善了功耗,性能和可伸缩性

- 可扩展到多集群实施

- 多个I/O一致性(IOCU)接口

- 具有256个中断的全局中断控制器(GIC)

- 高带宽256位内部数据路径和外部系统接口

- 集成的L2缓存(L2 $):16路集关联,最大8MB内存

- L2 $ RAM上的ECC选项可提供更高的数据可靠性

- 可配置的等待状态到RAM以实现最佳的L2 $设计

- L2 $硬件预取,可实现更高的吞吐量和性能

- 先进的电源管理

- 内核级DVFS(动态电压和频率缩放调整)–每个内核都可以以自己的时钟和电压电平独立运行

- 系统和SoC级别的虚拟化支持

- IOCU包括I / O MMU,GIC具有虚拟中断

- 在系统界面上给定 来宾ID,以集成到虚拟SoC设计中

- 先进的调试功能– PDtrace子系统允许查看内核和群集级别的跟踪信